Popular Keywords

- About Us

-

Research Report

Research Directory

Semiconductors

LED

Consumer Electronics

Emerging Technologies

- Selected Topics

- Membership

- Price Trends

- Press Center

- News

- Events

- Contact Us

- AI Agent

DDR5

News

[News] Taiwanese module maker Transcend Reportedly Sees 40–50% DDR5 Price surge in Q2

Amid recent price corrections in China’s retail DDR5 market that have raised concerns over a potential cooling in the memory cycle, Taiwan-based module maker Transcend pushed back against the narrative. According to Liberty Times, citing Chairman Peter Shu, the company’s actual transactions with...

News

[News] China’s DDR5 Price Drop Driven by Secondary-Market Modules; Impact Confined to Niche Channel

The recent DDR5 price correction in China’s retail market has triggered heated debate, with Calian Press reporting sharp spot-price declines of around 30% in Shenzhen’s Huaqiangbei Electronics Market, a key electronics trading hub. However, industry sources suggest the prices quoted by retailers...

Insights

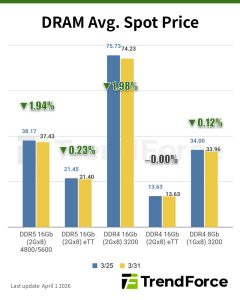

[Insights] Memory Spot Price Update: DDR3 Strength Contrasts Weak DDR4/ DDR5 Amid High Prices, Soft Demand

According to TrendForce's latest memory spot price trend report, regarding DRAM, momentum in both DDR4 and DDR5 remains weak, as end-user demand continues to struggle with elevated price levels, while 2Q26 contract pricing has yet to be formally announced. Meanwhile, in terms of NAND, module houses ...

News

[News] DDR5 Retail Prices Pullback Amid Market Correction, but Industry Players Cite Stable Contract Trends

Please note that this article cites information from Economic Daily News, Wccftech, 3D Center, chinastarmarket.cn and Calian Press. Recent sharp price corrections across U.S. and China retail memory channels have pushed DDR5 modules to the center of a broader sell-off, further fueled by market de...

News

[News] Select DDR5 Kits Reportedly Slide Over 20% in U.S. Retail Amid Google’s TurboQuant Debate

Please note that this article cites information from Wccftech, IT Chosun, and Tom’s Hardware. After months of relentless gains, the memory market might be showing early signs of a turning point. According to Wccftech, DDR5 prices have recently started to ease across several major U.S. retail chan...

- Page 1

- 11 page(s)

- 53 result(s)