[News] TSMC CoWoS Wafer ASP Reportedly Nears 7nm; Advanced Packaging to Become a Key Profit Driver

The AI compute race is heating up, pushing advanced packaging to the forefront, with TSMC’s CoWoS emerging as one of the most constrained resources in the global AI supply chain. According to Commercial Times, sources say the average selling price (ASP) of a single CoWoS wafer is around $10,000—on par with 7nm advanced process nodes—highlighting how packaging has entered a high-value competitive arena.

At the same time, supported by high ASPs and a relatively lower capital expenditure structure, CoWoS is seen as having the potential to achieve gross margins comparable to those of advanced process technologies, the report highlights.

The report states that although advanced packaging margins are currently below TSMC’s overall average, they are expected to become a key profit driver as economies of scale expand. Institutional investors project that TSMC’s capacity will reach about 1.3 million units in 2026 and could rise to 2 million in 2027, as supply accelerates to catch up with demand.

As the report notes, lower equipment depreciation is a key driver of profitability for advanced packaging. Equipment vendors cited in the report indicate that advanced nodes rely on EUV tools costing more than $150 million, whereas CoWoS, without requiring such costly front-end processes, carries a relatively lower capital expenditure per unit of capacity.

Further breaking down TSMC’s revenue structure, advanced packaging has been steadily increasing its contribution, reaching about 10% in 2025. With AI demand surging, this share is expected to continue rising, as the report indicates.

TSMC Maps Out Next-Gen Advanced Packaging Roadmap

TSMC is pushing forward its advanced packaging technologies. At its 2026 North America Technology Symposium, it outlined upgrade roadmaps for CoWoS and 3D stacking. According to another report from Commercial Times, TSMC noted that it is currently producing 5.5-reticle-size CoWoS and plans to introduce 14-reticle-size CoWoS by 2028. This would enable integration of around 10 compute dies and 20 HBM stacks, with further expansion of package size to follow and alignment with SoW-X (System-on-Wafer) technology.

In 3D ICs, TSMC is accelerating its SoIC roadmap, with A14-on-A14 SoIC targeted for production in 2029. The company says this will deliver 1.8× higher die-to-die I/O density compared with N2-on-N2 SoIC, enabling greater bandwidth for data transfer between stacked chips. The Commercial Times report adds that TSMC is also advancing co-packaged optics (CPO), adopting a COUPE-on-substrate approach for CPO solution, with production expected to begin in 2026.

Meanwhile, to keep advanced packaging close to its North American customers and capture orders from U.S.-based cloud service providers (CSPs), the report notes that TSMC plans to bring an advanced packaging facility online in Arizona by 2029.

TSMC has also significantly shortened the time to bring advanced packaging technologies into mass production. Commercial Times notes that SoIC deployment timelines have been reduced by up to 75%, accelerating customers’ time-to-market. Overall, advanced packaging capacity is projected to grow by about 80% from 2022 to 2027, underscoring how packaging has evolved from a back-end process into a key competitive lever for AI chips, the report adds.

Read more

- [News] TSMC 3nm Monthly Capacity May Hit 180K Wafers by 2026, Up Over 40% YoY on AI Demand

- [News] TSMC Latest Roadmap: A12, A13 for 2029 Without High-NA EUV; A16 Volume Production Delayed to 2027

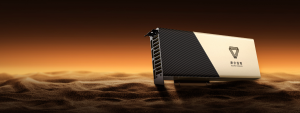

(Photo credit: TSMC)