[News] Samsung Leads in Unveiling BSPDN Research; TSMC and Intel Speed Up Deployment

As per a report from Taiwan’s TechNews,” TSMC, Samsung, and Intel have been actively deploying Backside Power Delivery Network (BSPDN) strategies recently, and have announced plans to incorporate BSPDN into their logic chip development roadmap. For instance, Samsung intends to implement BSPDN technology in its 2-nanometer chips, a move unveiled at the VLSI Symposium in Japan.

According to imec, BSPDN aims to alleviate the congestion issues faced by front-end logic chips in later-stage processes. Through Design Technology Co-Optimization (DTCO), more efficient wire designs are achieved in standard cells, aiding in the downsizing of logic standard cell.

In essence, BSPDN can be seen as a refinement of chiplet design. The conventional approach, where logic circuits and memory modules are integrated, is transformed into a configuration with logic functions on the front and power or signal delivery from the back.

While the traditional method of front-side wafer power delivery achieves its purpose, it leads to decreased power density and compromised performance. Nevertheless, the new BSPDN technique has not yet been adopted by foundries.

Samsung claims that, compared to the conventional method, BSPDN reduces area by 14.8%, providing more chip space for additional transistors and improved overall performance. Wire lengths are also cut by 9.2%, reducing resistance, allowing greater current flow, and thereby lowering power consumption while enhancing power transmission efficiency.

In June of this year, Intel also introduced its BSPDN-related innovations under the name ‘PowerVia.’ Team Blue plans to utilize this approach in the Intel 20A process, potentially achieving a chip utilization rate of 90%.

Intel believes PowerVia will address interconnect bottlenecks in silicon architecture, enabling continuous transmission through backside wafer powering. The company anticipates incorporating this novel approach into its Arrow Lake CPUs slated for release in 2024.

Furthermore, according to Taiwan’s supply chain sources, TSMC remains on track to launch its 2-nanometer process in 2025, with mass production expected in the latter half of the year in Hsinchu’s Baoshan. The company’s N2P process, planned for 2026, will feature BSPDN technology.

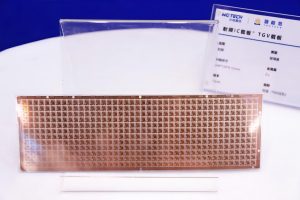

(Photo credit: Samsung)