Popular Keywords

- About Us

-

Research Report

Research Directory

Semiconductors

LED

Consumer Electronics

Emerging Technologies

- Selected Topics

- Membership

- Price Trends

- Press Center

- News

- Events

- Contact Us

- AI Agent

About TrendForce News

TrendForce News operates independently from our research team, curating key semiconductor and tech updates to support timely, informed decisions.

- Home

- News

[News] SK hynix Reportedly Develops HBM4 System-Level Testing Equipment, Deepens TSMC Collaboration

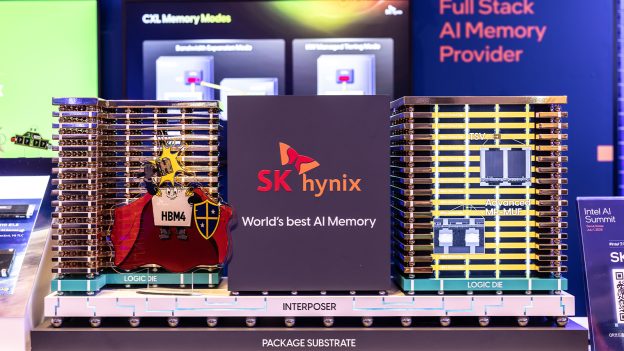

Competition in next-generation memory is heating up, and SK hynix is reportedly taking another step to reinforce its leadership in HBM4. According to The Elec, the company has successfully developed system-level testing equipment for its HBM4. The equipment enables memory makers to identify defects that may arise after HBM is integrated with AI chips—an evaluation process that had previously been handled by foundries.

Industry sources cited by the report say the new package-level testing equipment is designed to ensure HBM4 functions properly when integrated with GPUs or CPUs, and can be regarded as system-in-package (SiP) inspection equipment. The device passed SK hynix’s internal qualification testing last month.

System-level testing involves attaching a completed product to actual devices and equipment for evaluation, the report notes. In this case, the setup examines HBM installed alongside a customer’s system chip on a motherboard. As indicated by the report, the objective is to proactively verify inter-chip integration and compatibility before deployment.

As the report explains, system-level testing has traditionally been conducted primarily by foundries such as TSMC and Samsung Electronics, which oversee AI chipset packaging. However, as packaging technologies become more sophisticated and final-product yields grow increasingly important, memory companies are expanding their own system-level testing capabilities.

With its in-house HBM package-level testing, SK hynix can identify operational issues that emerge when GPUs and HBM are combined in real-world systems. The company shares validation data with customers to improve performance.

Notably, the report highlights that beginning with HBM4, the shift toward highly customized HBM solutions makes system-level compatibility verification increasingly essential to ensure seamless integration with each customer’s specific architecture.

SK hynix Advances HBM4 Strategy Alongside TSMC

SK hynix co-developed the HBM package tester with its partners, internalizing SiP inspection capabilities for HBM. The report adds that this move is viewed as part of deepening end-product collaboration among SK hynix, its customers, and foundries. It also notes that since 2024, SK hynix has worked closely with TSMC to address HBM4-related customer requirements, with TSMC’s SiP platform CoWoS (Chip-on-Wafer-on-Substrate) specifically optimized for HBM4.

The report further explains that SiP is a technology that integrates multiple system component chips, including CPUs, GPUs, and memory, into a single package. It is widely used for GPU-HBM integration in AI accelerators such as NVIDIA’s B200 and AMD’s MI355X, typically through 2.5D stacking on an interposer built over a semiconductor substrate.

Read more

- [News] NVIDIA GTC 2026 in Focus: Feynman Reportedly on TSMC A16, Samsung & SK hynix to Showcase HBM4

- [News] SK hynix Reportedly to Supply About Two-Thirds of NVIDIA HBM4; Samsung Targets Early Delivery

(Photo credit: SK hynix)