Popular Keywords

- About Us

-

Research Report

Research Directory

Semiconductors

LED

Consumer Electronics

Emerging Technologies

- Selected Topics

- Membership

- Price Trends

- Press Center

- News

- Events

- Contact Us

- AI Agent

About TrendForce News

TrendForce News operates independently from our research team, curating key semiconductor and tech updates to support timely, informed decisions.

- Home

- News

[News] Intel’s EMIB Reportedly Gains Traction with AI ASIC, Smartphone Clients, Could Package TSMC Dies

Recent reports that Apple and Qualcomm are recruiting engineers with EMIB (Embedded Multi-die Interconnect Bridge) expertise suggest Intel’s packaging technology is regaining momentum—helped in part by the tight squeeze on TSMC’s capacity. According to the Commercial Times, the shift indicates that Intel’s advanced-packaging solutions are increasingly entering the consideration set for smartphone SoC and AI ASIC customers.

Potential Strategic Partner for TSMC Chips

Notably, the report also cites chipmakers who say Intel is sharpening its focus on the advanced-packaging market and could even take in TSMC-fabricated dies for downstream packaging in the future—a move that would mark a significant expansion of Intel’s foundry ambitions.

Commercial Times notes that Intel holds a key advantage: advanced-packaging capacity on U.S. soil, from New Mexico’s Fab 9 and Fab 11x to potential future lines in Ohio. The report adds that EMIB’s support for heterogeneous die combinations allows highly customized designs—while domestic production gives Intel strategic weight well beyond cost, making it a natural downstream partner for TSMC’s Arizona-made chips.

EE Times reported in March that Intel Foundry VP of Packaging and Test, Mark Gardner, said the company is “working hard” to ease the advanced-packaging crunch. Gardner noted that much of the shortage stems from customers locked into competitor technologies [from TSMC], adding that Intel holds an advantage because it isn’t constrained by capacity. Notably, the report suggested that AWS and Taiwan’s MediaTek are among chip designers tapping Intel Foundry as a supplier.

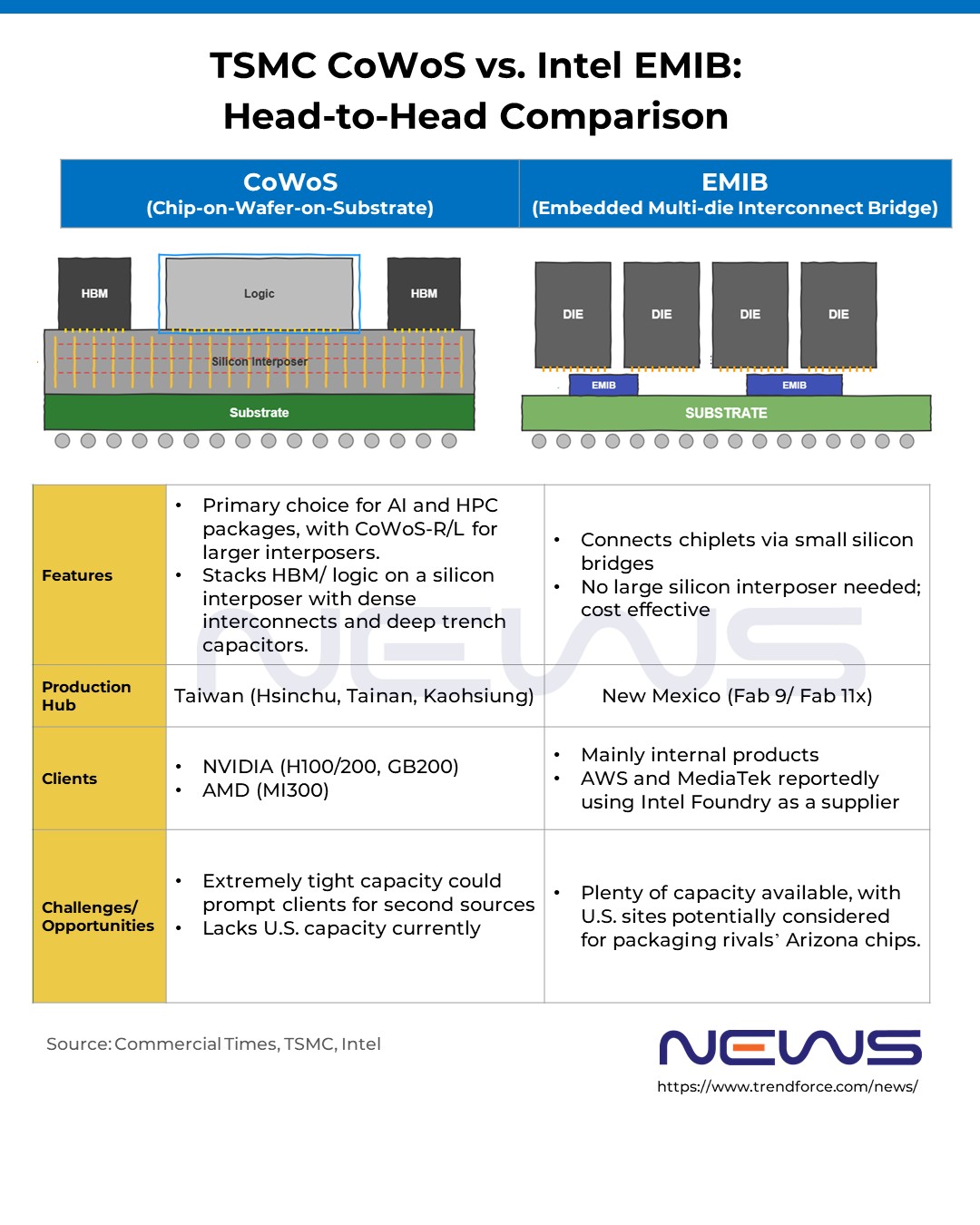

TrendForce notes that the AI and HPC data-center boom is driving unprecedented demand—creating a supply choke point at one major provider of advanced packaging. The crunch is spilling over to competitors, pushing major CSPs to look beyond CoWoS (Chip-on-Wafer-on-Substrate), with EMIB emerging as a serious contender, according to TrendForce.

More about Intel’s EMIB

Commercial Times explains that for now, TSMC’s CoWoS remains the top choice for AI GPU and HBM packaging, given its widespread use in NVIDIA’s H100/200, GB200, and AMD’s MI300 lineup. However, as the foundry giant’s advanced-packaging capacity remains in chronic shortage, Intel’s EMIB is emerging as a viable alternative.

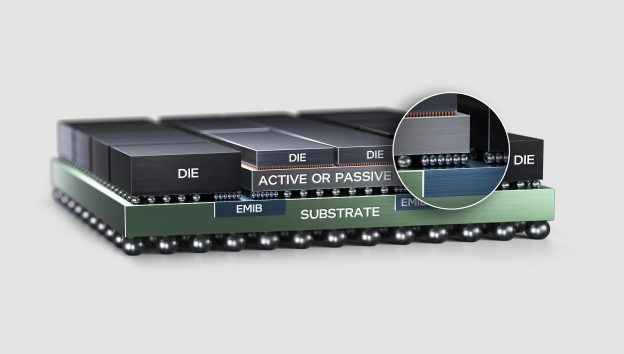

According to the report, unlike CoWoS, which uses a silicon interposer as the substrate, EMIB employs localized embedded bridges, offering better cost efficiency and greater design flexibility—making it well-suited for custom ASICs, chiplets, and AI inference processors.

Intel notes that EMIB is the industry’s first 2.5D interconnect solution using bridges embedded in the substrate. In high-volume manufacturing since 2017, EMIB features in products used in the server, network and HPC segments, the company states.

With rising demand for stronger power delivery, Intel Foundry has expanded its EMIB lineup. According to Intel, new EMIB-M integrates Metal-Insulator-Metal (MIM) capacitors directly into the silicon bridge to boost power performance. Surging demand for HBM has also increased the need for low-noise vertical power delivery, prompting Intel to introduce through-silicon vias (TSVs) in its EMIB-T solution—an approach that also eases migration from other packaging technologies.

On the other hand, Intel is also pairing EMIB with Foveros 2.5D and Foveros Direct 3D to create EMIB 3.5D, a hybrid architecture that stacks chiplets vertically using Foveros while linking them horizontally via EMIB’s embedded silicon bridge.

Read more

(Photo credit: Intel)