Popular Keywords

- About Us

-

Research Report

Research Directory

Semiconductors

LED

Consumer Electronics

Emerging Technologies

- Selected Topics

- Membership

- Price Trends

- Press Center

- News

- Events

- Contact Us

- AI Agent

About TrendForce News

TrendForce News operates independently from our research team, curating key semiconductor and tech updates to support timely, informed decisions.

- Home

- News

[News] TSMC Earnings Preview: $150B Capex Over Next Three Years Tops Five Key Focuses

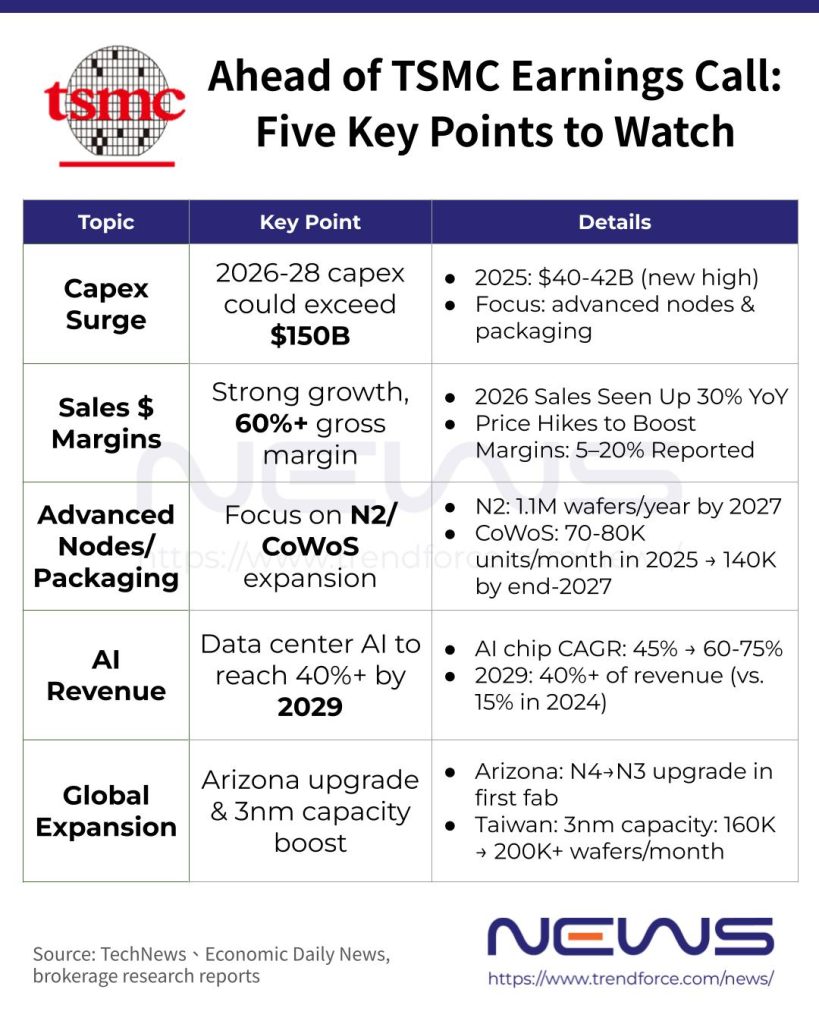

Ahead of TSMC’s earnings call on January 15, the market has already been flooded with reports that the company may build five additional fabs in Arizona under a U.S.–Taiwan trade framework. But what else should investors be watching when results are released tomorrow?

A TechNews report flags five key issues. Citing major institutional houses including Morgan Stanley, Goldman Sachs, JPMorgan and Nomura, it says TSMC’s capital spending could exceed US$150 billion over the next three years.

Capex Surge

As previously reported by the Economic Daily News, TSMC’s 2025 capital spending is expected to reach a new high in the range of US$40 billion to US$42 billion. Now, Fubon and Morgan Stanley, cited by TechNews, project its spending could jump to US$50–52 billion in 2026 — potentially higher — with 2027 expected to top US$55 billion. JPMorgan goes further, forecasting total capex from 2026 onward could exceed US$150 billion over three years.

Most of this massive investment is aimed at advanced processes and packaging, highlighting TSMC’s confidence in long-term AI chip demand from major customers such as NVIDIA and Broadcom, TechNews suggests.

Revenue and Profit Outlook: Strong Growth, Higher Margins

Research houses cited by TechNews expect TSMC to maintain strong growth from 2025 to 2027. Nomura stands out as particularly bullish, forecasting a 31.4% year-on-year sales increase in 2026.

On profitability, most sell‑side analysts cited by TechNews see gross margin holding above 60% in 2026. JPMorgan notes that as 3nm (N3) yields improve, margins should return to the company’s long-term average, while 2nm (N2) is expected to be even more profitable. Market chatter also points to possible price hikes of 5–10% for N5 and N3 in January 2026, helping to further support TSMC’s margins, as noted by TechNews.

Another Economic Daily News report confirms TSMC’s price uptrend, noting the foundry has notified customers of a four-year consecutive wafer price hike. 2026’s increase is already set at 5–20% and is expected to continue beyond the post-Trump period, the report adds.

TSMC’s N2 and CoWoS Expansion in Focus

TSMC’s technology moat remains firmly intact as it pushes ahead on both leading-edge processes and advanced packaging. Goldman Sachs, cited by TechNews, notes that N2 revenue is likely to outpace early N3 growth. Fubon estimates TSMC’s annual N2 capacity will exceed 1.1 million wafers by 2027, with Apple expected to be the first adopter in 2026.

Notably, major institutional houses also agree that with AI accelerator supply still tight, TSMC is rapidly expanding CoWoS (Chip-on-Wafer-on-Substrate) capacity. Fubon projects its monthly CoWoS output will reach around 140,000 units by the end of 2027. Nomura, on the other hand, expects AI ASICs to begin adopting SoIC (System-on-Integrated-Chips) in 2027, while Apple is seen introducing WMCM (Wafer-Level Multi-Chip Module) packaging in 2026.

According to the Economic Daily News, TSMC’s CoWoS output in 2025 is roughly 70,000–80,000 units, doubling 2024’s 30,000, with 2026 projected to hit 110,000–120,000 units.

Data Center AI Could Account for 40% of Revenue

TechNews points out that while TSMC previously guided for an AI chip revenue CAGR of around 45%, most foreign brokerages now view that as conservative. Morgan Stanley, being optimistic, expects TSMC to raise its AI foundry revenue growth outlook to 60% or even 75%.

Goldman Sachs, meanwhile, forecasts that by 2029, data center AI chips will contribute more than 40% of TSMC’s total revenue — up from the mid-teens level, or roughly 15%, in 2024, according to TechNews.

Global Footprint and New Capacity Build-Out

While potential additional Arizona expansion may bring uncertainties, TechNews highlights TSMC’s ambitious U.S. plans: its first Arizona fab could be upgraded directly from N4 to N3 in 2026, with the second fab’s mass-production timeline possibly moved up.

According to the Economic Daily News, surging AI and high-performance computing demand has triggered a flood of 3nm orders, forcing TSMC to revise its capacity plans. Originally, three new 2nm fabs were planned at Tainan 18B, but the focus has reportedly shifted to 3nm. Similarly, Phase 2B at Arizona Fab 21, initially slated for 2nm, will now start with 3nm, the report adds.

The Economic Daily News also notes that under the expanded 3nm plan, TSMC’s monthly output is expected to rise from the originally planned 160,000 wafers to over 200,000.

Read more

- [News] TSMC Reportedly Plans 5 More Fabs in Arizona Under U.S. Trade Deal, Investment Could Top $100B

- [News] TSMC Reportedly Suspends New 3nm Kick-offs, Steers Customers to 2nm to Optimize Costs

(Photo credit: TSMC’s LinkedIn)