[News] SK hynix Unveils 5-Bit NAND That Splits Cells, Delivers 20× Faster Reads

Memory giants are treading carefully on NAND capacity expansion and phasing out older products like MLC (Multi-Level Cell), while doubling down on advanced technologies. Notably, at the San Francisco 2025 IEDM conference in December, SK hynix unveiled its cutting-edge 5-bit NAND flash, claiming read speeds up to 20× faster than conventional PLC (Penta-Level Cell) flash, Blocks & Files reports.

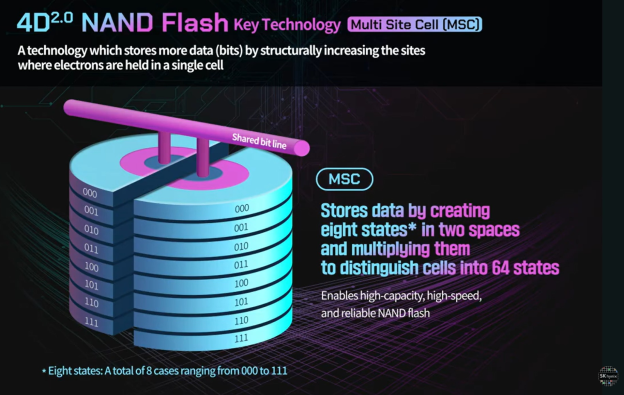

The approach of SK hynix, known as Multi-Site Cell (MSC) NAND technology, splits each 3D NAND cell in half, raising the data capacity per cell while cutting the number of voltage states by roughly two-thirds, according to the report.

Blocks & Files notes that the breakthrough showcases SK hynix’s 4D 2.0 technology, in development since 2022. The innovation tackles a major NAND bottleneck—traditional cells hit a “voltage state barrier” beyond four bits (QLC). By redesigning how bits are stored, SK hynix can now fit five bits per cell without compromising speed or endurance, the report adds.

Cracking the Cell Code: SK hynix’s Multi-Site Cell Approach

The report explains that adding more voltage states—distinct voltage levels that a memory cell can hold to represent data—squeezes them closer together, shrinking the sensing margin and making them harder to distinguish accurately. Simply put, packing more bits into a cell wears it out faster, reducing both reliability and endurance.

Today, QLC 3D NAND flash is already in mass production, but penta-level cell (PLC) technology hasn’t gone commercial yet, due to low read reliability and shorter lifespan, the report notes. Still, the report suggests PLC is highly attractive, as it could increase a NAND die’s capacity—and SSD storage—by up to 25% compared with current QLC chips.

Thus, SK hynix tries to tackle the bottleneck by splitting a NAND cell into two independent “sites,” each with fewer voltage states, and combines the two sites’ values to store more bits.

As noted by the report, under SK hynix’s framework, each half-cell—or “site”—has six voltage states. By combining the two sites, the overall system produces 36 possible voltage states, more than enough to encode the 32 states required for PLC flash, with four states left unused, which allows SK hynix to pack five bits per cell while maintaining reliability, the report notes.

Read more

- [News] SK hynix Reportedly Aims 100 Million IOPS with AI-NAND by 2027 in Collaboration with NVIDIA

- [News] SK hynix Reportedly Accelerates Hybrid Bonding for 300-Layer V10 NAND, Eying 2027 Mass Production

(Photo credit: SK hynix’s YouTube)