[News] Intel’s Clearwater Forest Unveils 18A Backside Power at Hot Chips; TSMC’s Super Power Rail to Follow

At Hot Chips 2025 (Aug. 24–26), Intel unveiled its next-generation Xeon processor, Clearwater Forest, which is built on 18A and scheduled for mass production in 2026, according to the Commercial Times.

Notably, while Intel’s new E-core Xeon integrates 18A with Foveros Direct 3D advanced packaging, Commercial Times highlights that Team Blue will also introduce PowerVia, its backside power delivery technology (BSPDN), in its 18A node.

As Intel explains, the industry-first PowerVia technology relocates course pitch metals and bumps to the back side of the die and embeds nano-scale through-silicon vias (nano-TSVs) in every standard cell for efficient power distribution. The new structure, according to Intel, improves standard cell utilization by 5-10% and ISO-power performance by up to 4%.

According to Tom’s Hardware, Clearwater Forest marks one of the first deployments of Intel’s 18A node, built on RibbonFET transistors and backside power delivery. By separating power and signal paths, Intel says the chip uses energy more efficiently and keeps voltage drops low—critical for hyperscalers running massive, power-hungry data centers, the report adds.

While the 18A node will remain primarily for internal products, Intel’s roadmap points to 14A, which will adopt PowerDirect, a direct-contact power delivery method that builds on the PowerVia architecture, according to its press release.

TSMC Super Power Rail Roadmap

On the other hand, Commercial Times points out that TSMC is expected to roll out its A16 process—also introducing backside power delivery—in the second half of next year, with supply chain players gearing up. According to TSMC, its A16 node integrates leading nanosheet transistors with innovative Super Power Rail (SPR) solutions, which improves logic density and performance by dedicating front-side routing resources to signals.

Compared to TSMC’s N2P process, A16 will provide an 8-10% speed improvement at the same Vdd (positive power supply voltage), a 15-20% power reduction at the same speed, and up to 1.10X chip density, it states.

Following A16, TSMC also plans to bring backside power delivery to its next advanced node, A14, slated for production in 2028. However, Tom’s Hardware notes the first version will launch without BSPDN, with an enhanced version incorporating the technology expected in 2029.

Read more

- [News] Intel 18A Yield Reportedly Just 10% at Risk Production, Casting Doubt on Panther Lake Plans

- [News] TSMC Tech Symposium Highlights: A14 Set for 2028 Launch; 9.5 Reticle CoWoS Arriving in 2027

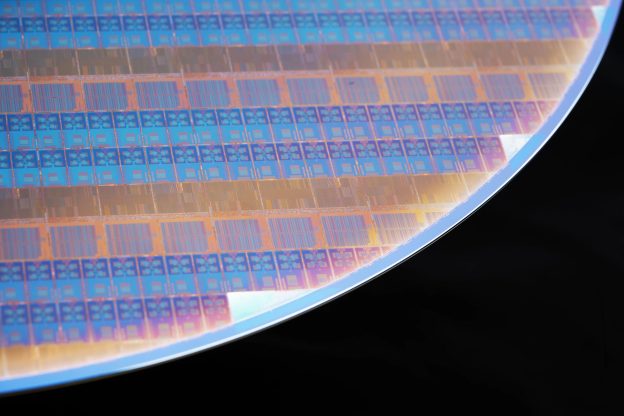

(Photo credit: Intel)