Popular Keywords

- About Us

-

Research Report

Research Directory

Semiconductors

LED

Consumer Electronics

Emerging Technologies

- Selected Topics

- Membership

- Price Trends

- Press Center

- News

- Events

- Contact Us

- AI Agent

About TrendForce News

TrendForce News operates independently from our research team, curating key semiconductor and tech updates to support timely, informed decisions.

- Home

- News

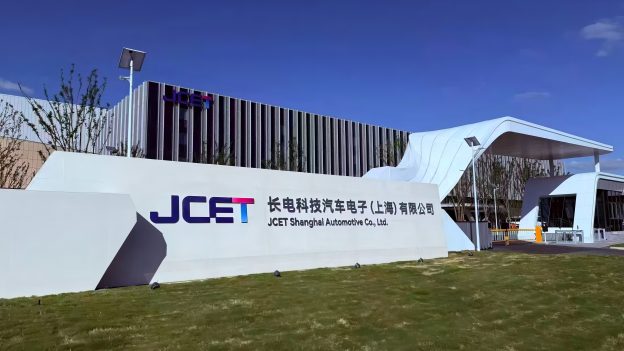

[News] CPO Emerges as the New Sought-After as JCET and UMC Secure Early Position

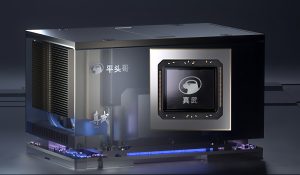

On January 21, JCET announced a major breakthrough in its co-packaged optics (Co-Packaged Optics, CPO) technology development.

Silicon photonics engine products based on its XDFOI® multidimensional heterogeneous advanced packaging platform have completed customer sample deliveries and successfully passed client-side validation and testing.

As artificial intelligence and high-performance computing workloads continue to grow rapidly, system demand for optical interconnect technologies featuring higher bandwidth, lower latency, and improved energy efficiency is intensifying. By leveraging advanced packaging to achieve microsystem-level integration of photonic and electronic devices, CPO offers a more compact and energy-efficient path for next-generation high-performance computing systems.

CPO is expected to play a pivotal role in both scale-up and scale-out network architectures and is widely regarded as a cornerstone of next-generation computing infrastructure. Meanwhile, as different segments of the silicon photonics supply chain advance in coordination, the CPO ecosystem is gradually taking shape, spanning critical stages from design and manufacturing to packaging, testing, and system-level validation.

Notably, foundry giant United Microelectronics Corporation (UMC) is also actively deploying CPO technology, with mass production targeted for 2027.

It’s reported that UMC is executing an upgrade strategy for its mature process nodes, positioning itself squarely for the CPO era.

In recent years, the company has focused on enhancing the value proposition of mature nodes by steering its 22/28 nm processes toward more competitive specialty applications. Market sources indicate that UMC’s Fab 12i Phase 3 facility in Singapore plays a critical role in this strategy.

The new fab centers its operations on 22/28 nm technologies, serving applications across communications, automotive, IoT, and AI markets, while further strengthening UMC’s in CPO-related applications. Sources note that the fab’s 22 nm production line already provides a mature process foundation capable of supporting silicon photonics products.

In response to market inquiries regarding progress, UMC officially confirmed that silicon photonics is indeed one of the company’s key focus technologies within its specialty process roadmap. Industry sources further reveal that optoelectronic integration modules are already being planned in parallel, with risk production expected to begin in 2026 and full-scale mass production targeted for 2027.

To accelerate commercialization, UMC has adopted a strategy of strategic collaboration. The company recently announced the signing of a technology licensing agreement with IMEC, the world-leading semiconductor R&D and innovation hub based in Belgium. Through this partnership, UMC has introduced IMEC’s proven “iSiPP300” silicon photonics process platform.

Industry analysts point out that as AI-driven data traffic continues to surge, traditional copper interconnects are increasingly constrained by bandwidth and power consumption limitations. By co-packaging optical engines directly with computing chips, CPO technology dramatically shortens electrical signal transmission distances.

Compared with conventional pluggable optical modules, CPO offers clear advantages in reducing power consumption and latency, lowering reliance on power-hungry digital signal processors (DSP) and long copper traces, and significantly improving bandwidth density—making it a compelling solution for meeting the ultra-high bandwidth demands of next-generation data centers.

(Photo credit: JCET on LinkedIn)